Características importantes

- Coste por pin < 100 USD

- CPU dedicada por DUT

- Una sola placa con todos los recursos A/D para testear un DUT

- Hasta 1.152 canales analógicos/digitales

- Integración en el estímulo MEMS, acoplamiento duro/blando con manejador/probador, uso de benchtop

Testers orientados a dispositivos MEMS

Ponemos un tester en el tamaño de una tarjeta postal

¿Están tus requisitos de test orientados a familias definidas de dispositivos, con características comunes? No necesitas comprar un costoso tester de señales mixtas de propósito general: puedes confiar en SPEA DOT 100, un sistema diseñado para responder a los requisitos de test de MEMS y otros dispositivos de bajo número de pines a un coste increíblemente bajo.

El DOT 100 se basa en una revolucionaria arquitectura por dispositivo: cada dispositivo bajo test tiene una CPU dedicada que maneja todo el proceso de test, mientras que cada placa aloja todos los recursos para el test paralelo de 6 dispositivos, en el tamaño de una tarjeta postal.

Todo esto está contenido en un tamaño transportable en la mano, que se puede integrar en el estímulo MEMS de SPEA, acoplado duro/blando con probador o manejador, o se puede utilizar como unidad de benchtop.

Test paralelo rápido multisitio

Test paralelo rápido multisitio

- CPU dedicada por dispositivo

- Hasta 1.152 canales analógicos/digitales

- Alimentación de dispositivos y unidad de medición de tiempo por dispositivo

- Memoria de modelo por canal (30 Mstep)

- Capacidades digitales asíncronas

- Unidades lógicas programables (SPI, I2Cbus, Uart, Puerta de I/O)

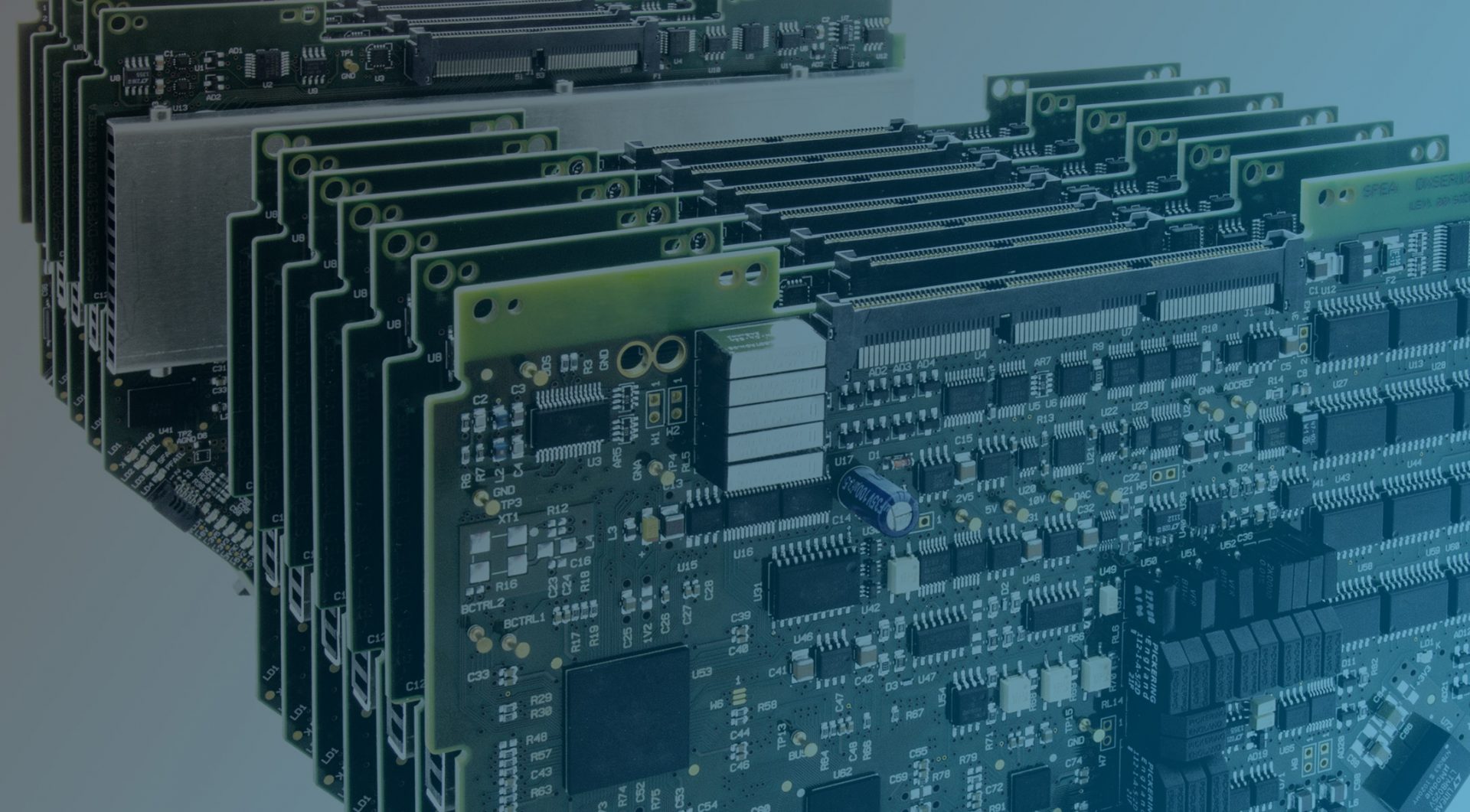

Electrónica de pin de ultra alta densidad

Electrónica de pin de ultra alta densidad

En el núcleo de los testers de DOT hay la electrónica de pines, que provea 48/96 canales en 3/6 secciones independientes.

Cada sección contiene:

- 8 canales digitales @ 5 Mhz & 8 canales analógicos (DPS) hasta 10 V; 256 mA (manejador y digitalizador por pin)

- 8 canales digitales @ 50 MHz + 1 canal analógico (manejador y digitalizador multiplexado)

- 2 unidades de medida de tiempo

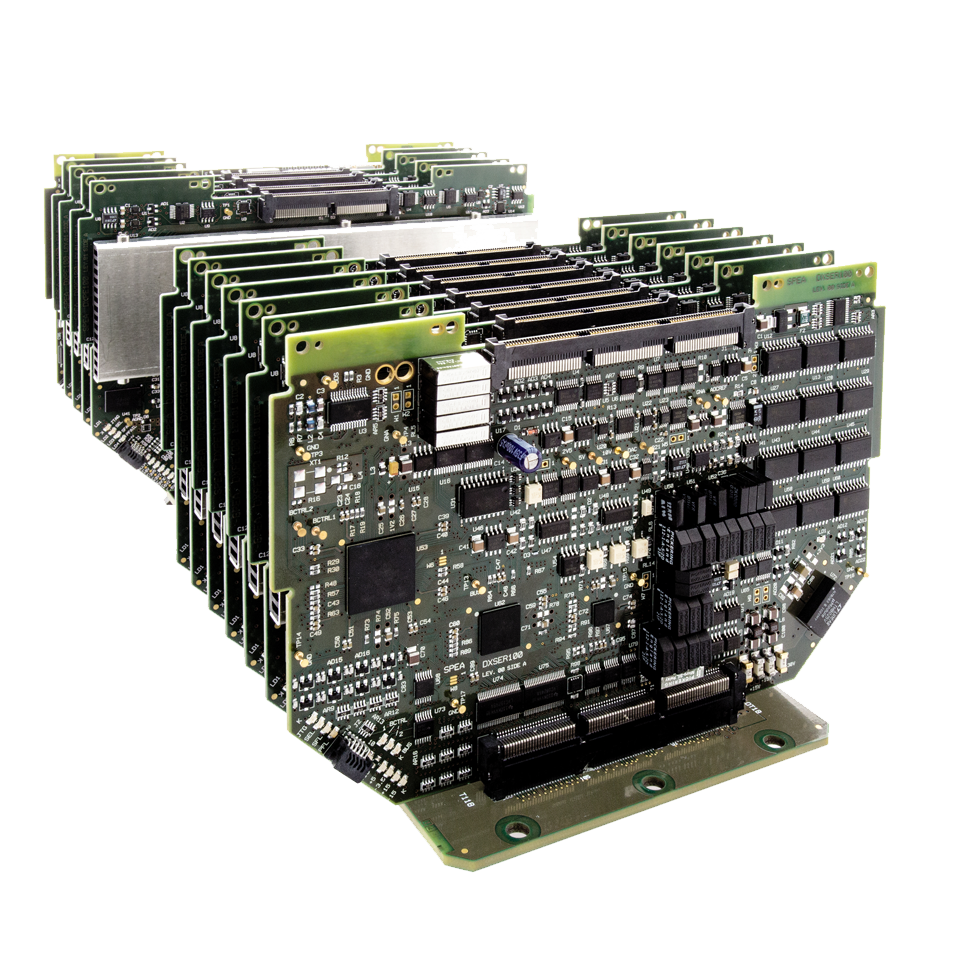

Concepto de test final paralelo completo

Concepto de test final paralelo completo

Las células de test SPEA realizan el test paramétrico y funcional completo en los dispositivos completamente encapsulados, al final del proceso de producción.

Después del test, los productos se pueden enviar directamente al cliente, sin necesidad de trabajar o volver a testear.

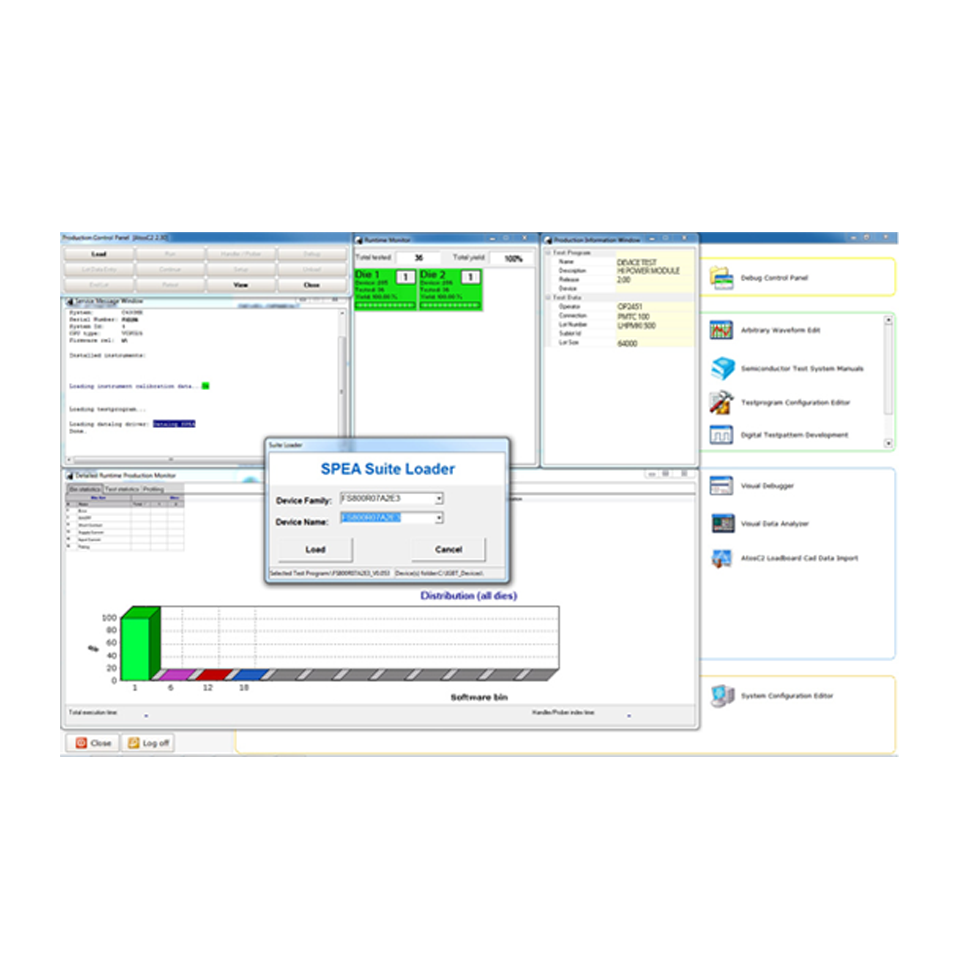

Generación y depuración del programa de test < 1 día

- Entorno de programación fácil de aprender

- Generación del programa de test guiada

- La generación automática de códigos reduce drásticamente el tiempo necesario para desarrollar, depurar y lanzar el programa

- Importación automática de datos

- Bibliotecas de instrucciones orientadas al DUT y orientadas al instrumento

- Mapa de DUT

- Desarrollo de aplicaciones muy rápido

- Analizador de resultados de test

- Shmoo Plot

- Fácil de realizar. Fácil de seguir. Fácil de mantener.